# Development of Novel System and Component Architectures for Future Innovative 100 GBit/s Communication Systems

Christian Carlowitz

Friedrich-Alexander Universität Erlangen-Nürnberg

christian.carlowitz@fau.de

research supported by German Research Foundation (DFG), SPP 1655

#### **Project Partners**

- Prof. Dr.-Ing. Martin Vossiek

Institute of Microwaves and Photonics (LHFT)

Friedrich-Alexander Universität Erlangen-Nürnberg

- Prof. Dr.-Ing. Dr.-Ing. habil. Robert Weigel Institute of Electronics Engineering (LTE) Friedrich-Alexander Universität Erlangen-Nürnberg

- Prof. Dr. sc. techn. habil. Frank Ellinger

Chair of Circuit Design and Network Theory (CCN)

Technische Universität Dresden

- Prof. Dr.-Ing. Manfred Berroth Institute of Electrical and Optical Communications Engineering (INT) Universität Stuttgart

Universität Stuttgart

## Outline

- 1. Introduction

- Motivation

- SPARS Concept

- Transceiver Architecture

- 2. Project Topics

- LHFT: System Concept Investigation and Experimental Verification

- CCN: 180 GHz SPARS Receiver Frontend Design

- LTE: 180 GHz QAM Modulator and High Speed DAC Design

- INT: High Speed Receiver Analog Baseband Architectures and Design

- 3. Conclusion

#### **Motivation**

- High speed communication systems:

- Symbol rate up to 20% of carrier

- − e.g. 2x18 GBaud at 180 GHz  $\rightarrow$  > 100 GBit/s wireless

- Technological limitations:

- Operation close to process transit frequency

- $\rightarrow$  Low single-stage amplifier gain

- Scaling issues: Long amplifier chains, high area cost, high power dissipation

- Goal: Scalable, efficient and broadband *quadrature* transceivers beyond homodyne architectures

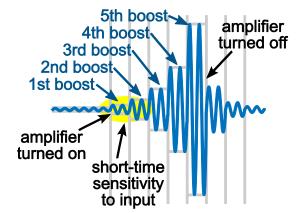

# SPARS - "Simultaneous Phase and Amplitude Regenerative Sampling" - A disruptive technology

The ordinary approach

Gain:  $g_t = g^N$

Example (with *N*=5; g = 2):  $\Rightarrow g_t = 32$

Power dissipation:

$$P_{d_{total}} = 5 \cdot P_d$$

Power consumption and complexity dramatically reduced, especially useful when working close to transit frequency

SPARS / SRO approach sampling clk. (on/off switch)  $g \rightarrow g_t \cdot \operatorname{III}_{T_{SW}}(t) \cdot s(t)$ Gain (pos. feedback):  $g_t = \sum_{l=1}^{L} g^l$ Example: (with L=4; g = 2):  $\Rightarrow g_t = 30$  $P_{d_{total}} = P_d$ Power dissipation: 5th boostamplifier 4th boost turned off 3rd boost 2nd boost 1st boost amplifier turned on short-time sensitivity to input

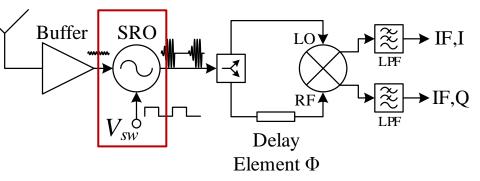

#### **System Concept**

- Novel Transceiver Architecture: "SPARS", Simultaneous Phase and Amplitude Regenerative Sampling

- Major Benefits: Overcome scaling and power dissipation issues by:

- High gain boost with single stage amplifier (6 dB  $\rightarrow$  30 dB)

- No PLL, no stabilized LO, no LNA or PA chains

- Employing self-mixing receiver approach

- Relaxing modulator power level requirements

WS-03 | Wireless 100Gb/s and Beyond: Progress in Ultra-fast Wireless Communications

## System Concept Investigation and Experimental Verification

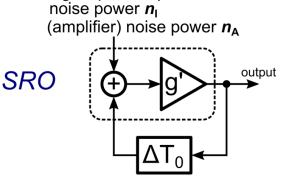

## Noise Figure, SNR/Sensitivity

- Super-regenerative oscillator vs. amplifier chain

- Difference:

- amplifier chain adds noise after each stage:  $F_{ac} = F + \sum_{k=1}^{n-1} \frac{F-1}{G^k}$

- SRO adds signal and noise at each oscillation cycle:

- Noise bandwidth?

- homodyne receiver: symbol rate is lower bound (with sinc-shaped pulses, rect. filter)

- super-regenerative theory:

→ similar performance achievable

- at technological boundaries:

2-4 dB excess

- overall: SRO and amplifier chain comparable / slight SRO advantage

# $\begin{array}{c} amplifier chain \\ (amplifier) & (amplifier) \\ noise power <math>n_A$ noise power $n_A$ signal $\square$

signal power s<sub>I</sub>

noise

power *n*

**EuMC**

$F_{sro} = F$

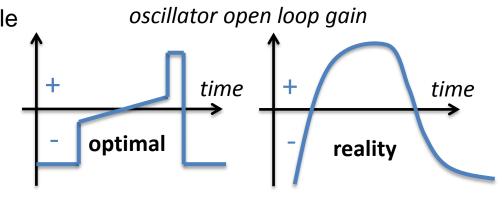

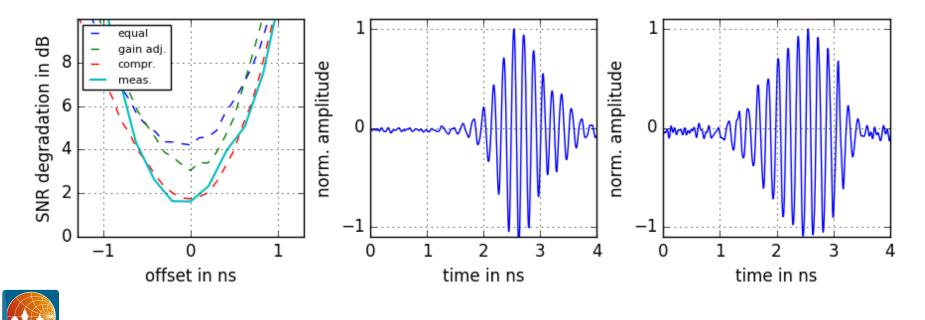

#### **Pulse Recovery**

- SRO samples *average* input power during sensitivity phase

- countermeasures (if peak power limited):

- gain tuning  $\rightarrow$  faster rise, shorter sampling period

- slight compression  $\rightarrow$  widens peak maximum

- quench signal shaping  $\rightarrow$  hold unity gain on decay

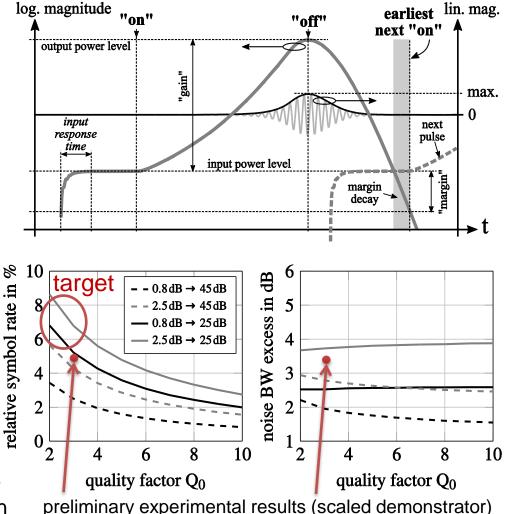

#### **Achievable Data Rate**

- Minimum period: Oscillation rise and decay + SNR margin

- Dependencies:

- oscillator tank quality factor Q<sub>0</sub>

- active element gain M

- Typically low open loop gain (e.g. < 3 dB)</li>

- Rise time limitation (T=2/f<sub>0</sub> ... 4/f<sub>0</sub>) included in simulation

- Results:

- 10x gain with 8-10% relative symbol rate could be achieved

- Preliminary experimental result with scaled demonstrator

- 270 MBaud measured @ 5.8 GHz

- 293 MBaud theoretical expectation

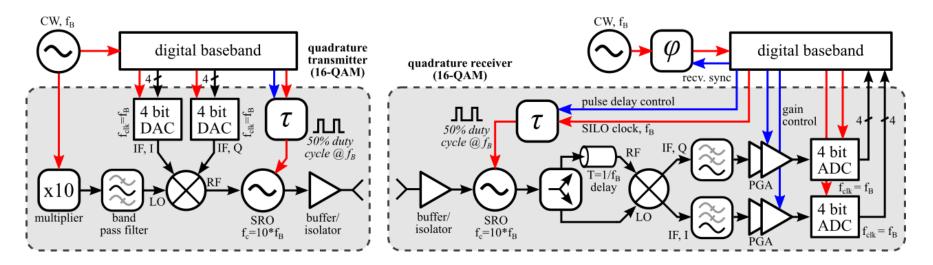

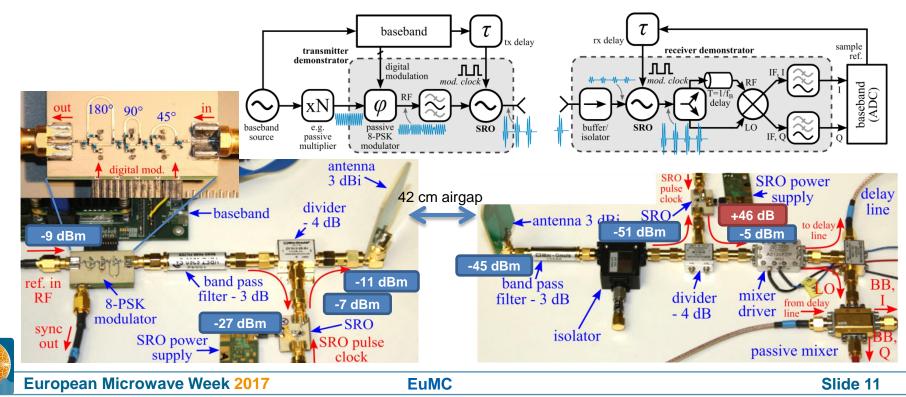

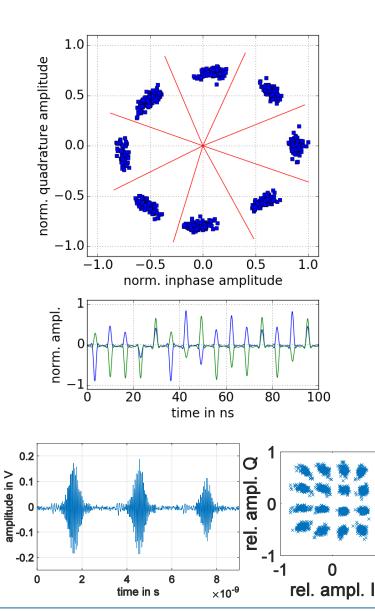

#### **Demonstrator Implementation**

- Complete transmitter and receiver at 5.8 GHz, 150 MBaud (450 MBit/s)

- passive 8-PSK modulator (diode switched transmission lines, 11 dB loss)

- discrete SRO (electrically small, single port)

- filter/antenna from COTS components (~10 dB loss)

- Receiver: Isolator at input, self-mixing with cable delay line

#### **Demonstrator Measurement Results**

- Complete Transmitter & Receiver:

- Modulation: 8-DPSK

- EVM < -18 dB (BER < 10<sup>-3</sup>)

- diff.: EVM < -21 dB

- Measured Deviations:

- TX EVM -30 dB (systematic)

- RX EVM -24 dB (stochastic)

- Sensitivity CW: -77 dBm, pulsed: -75 dBm

→ close to theoretical SNR=P<sub>s</sub>/(k\*T\*B\*F)

- 24 GHz 16-QAM Demonstrator (SRO only):

- 343 MBaud (1.37 GBit/s)

- 5 dB single stage gain

→ 25 dB

- linear recovery of amplitude and phase

WS-03 | Wireless 100Gb/s and Beyond: Progress in Ultra-fast Wireless Communications

## **180 GHz SPARS Receiver Frontend Design**

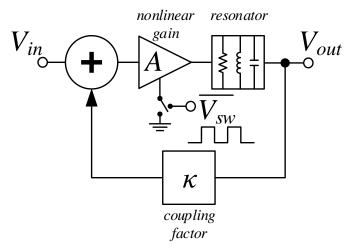

#### Integrated mm-Wave Super-Regenerative Oscillators (mmW SROs)

- Most amplification is done in SRO component

- Many design compromises possible e.g. gain, symbol rate, dynamic range, etc.

- Proper modelling of SRO circuit provides guidelines for performance optimization

- Large-signal behavior is of highest importance

- Study relation between V<sub>out</sub> and V<sub>in</sub> in phase and amplitude

- Model implemented electrically using CAD tools

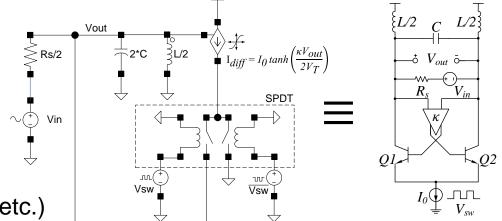

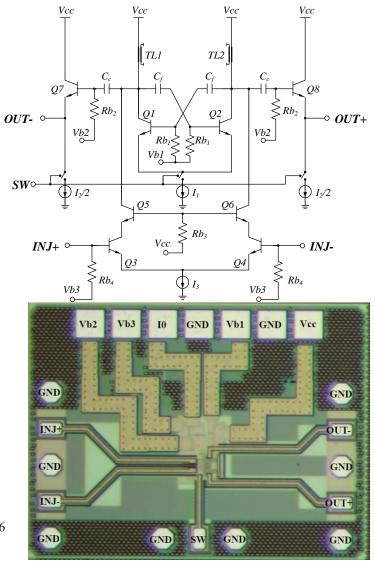

- Cross-coupled topology chosen for monolithic integratibility

#### **Proposed Regenerative Receiver**

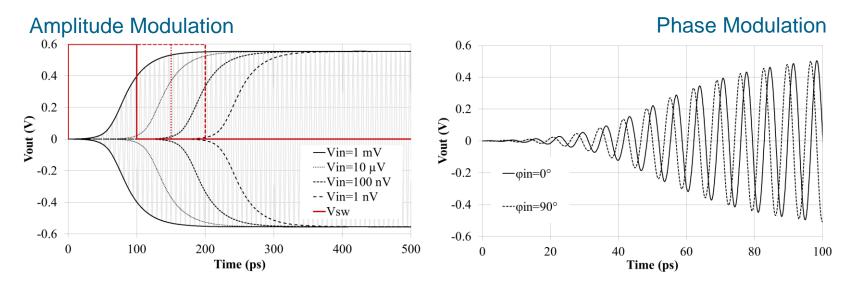

#### Modeling of integrated mmW SROs

- Ideal nonlinear model; no base currents, numerical simulations

- Amplitude and phase sampling

- Influence of design variables on performance can be studied

(e.g. loop gain, RC time constant, etc.)

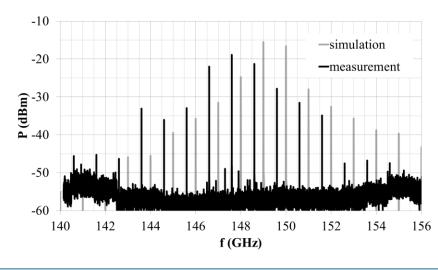

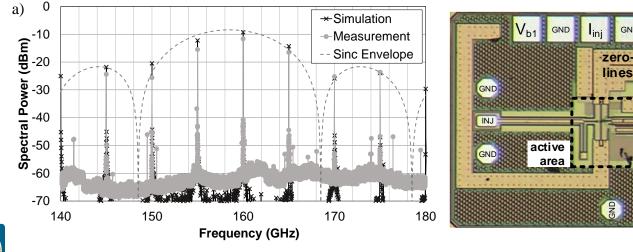

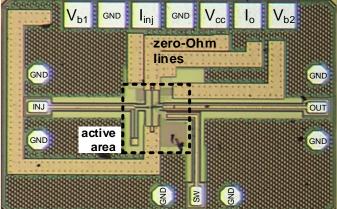

#### Cross-Coupled mmW SRO in IHP 0.13-µm SiGe BiCMOS

| f <sub>osc</sub> (GHz)  | 148  |

|-------------------------|------|

| P <sub>DC</sub> (mW)    | 48   |

| f <sub>sw</sub> (GHz)   | 1    |

| P <sub>out</sub> (dBm)  | -6   |

| Area (mm <sup>2</sup> ) | 0.66 |

| Gain (dB)               | 36   |

**European Microwave Week 2017**

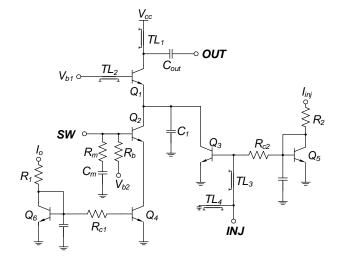

#### Single-Ended Colpitts mmW SRO in IHP 0.13-µm SiGe BiCMOS

| f <sub>osc</sub> (GHz)  | 160  |

|-------------------------|------|

| P <sub>DC</sub> (mW)    | 6.6  |

| f <sub>sw</sub> (GHz)   | 5    |

| P <sub>out</sub> (dBm)  | -8.4 |

| Area (mm <sup>2</sup> ) | 0.64 |

| Gain (dB)               | 18.4 |

**European Microwave Week 2017**

WS-03 | Wireless 100Gb/s and Beyond: Progress in Ultra-fast Wireless Communications

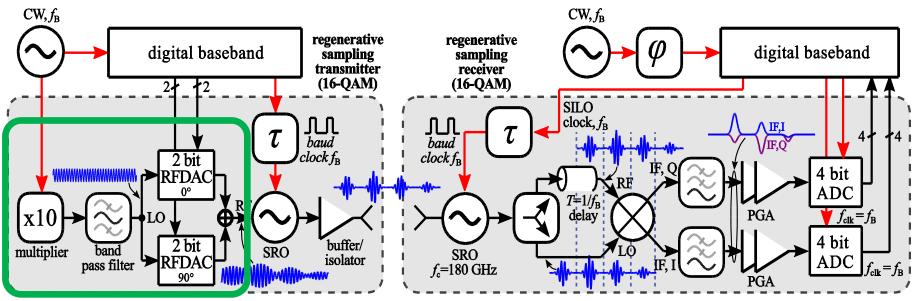

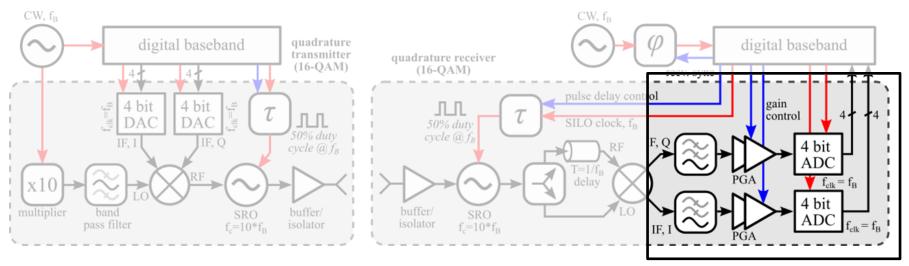

# 180 GHz QAM Modulator and High Speed DAC Design

#### **SPARS** based frontend

#### Functionality

- Generates 180 GHz carrier frequency with a times ten frequency multiplier

- 16 QAM modulation achieved via two radio-frequency Digital-to-Analog Converters of 2 bit each with a modulation rate of up to 18 GS/s

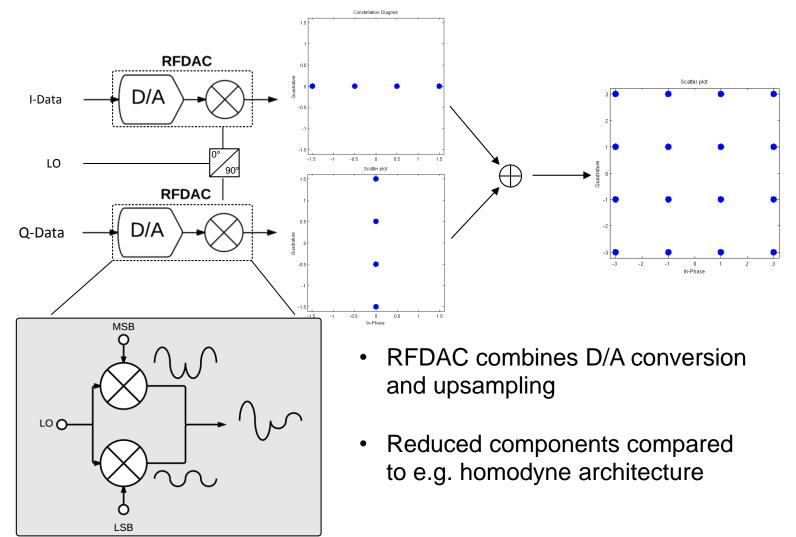

#### Radio-Frequency Digital-to-Analog Converter

#### **Radio-Frequency Digital-to-Analog Converter**

- Current steering principle

- Better spectral purity and wider bandwidth

- Upsides

- Rejection of all outputs at DC and even harmonics of f<sub>LO</sub>

- All transistors act as switches, hence no linearity constraints

- Linearity of output signal defined by:

- Resolution of converter

- Output impedance modulation

- Mismatch in timing

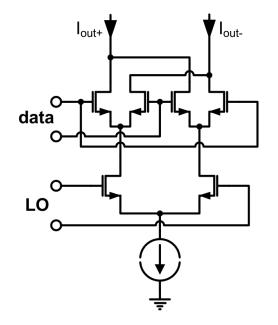

Example of RF-DAC output stage

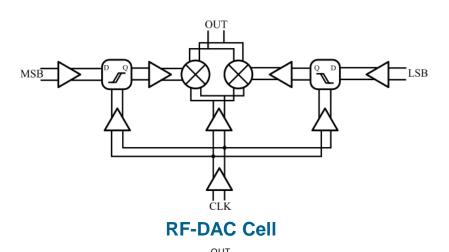

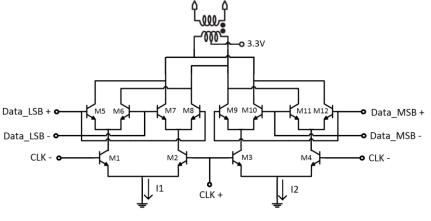

#### Design of a 2 bit 180 GHz RF-DAC for SPARS

- Each RF-DAC consists of three identical RF-DAC cells

- Current summation at the output via broadband transmission lines

- Buffers for signal boosting and for blocking of clock feed through

- Flip-Flops for retiming purposes

- Output stage of each RF-DAC cell features two parallel connected Gilbert cells working as BPSK modulators

- Ratio between the transistors and currents of the two Gilbert cells to be 3:1

- Transformer increases linearity and SNR

**RF-DAC** output stage

WS-03 | Wireless 100Gb/s and Beyond: Progress in Ultra-fast Wireless Communications

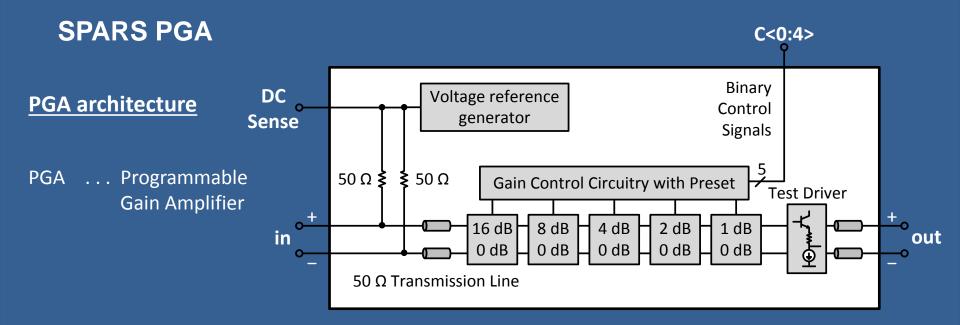

## High Speed Receiver Analog Baseband Architectures and Design

#### **SPARS** baseband receiver

Analog baseband receiver

## **Functionality**

- Digitization of wideband inphase (I) and quadrature (Q) receive signals (> 9 GHz) by PGA+ADC solution

- External data storage on FPGA to ensure a sufficient number of receive samples for

- system demonstration experiments and

- evaluation of link synchronization parameters (e.g., I/Q gain and phase mismatches, etc.)

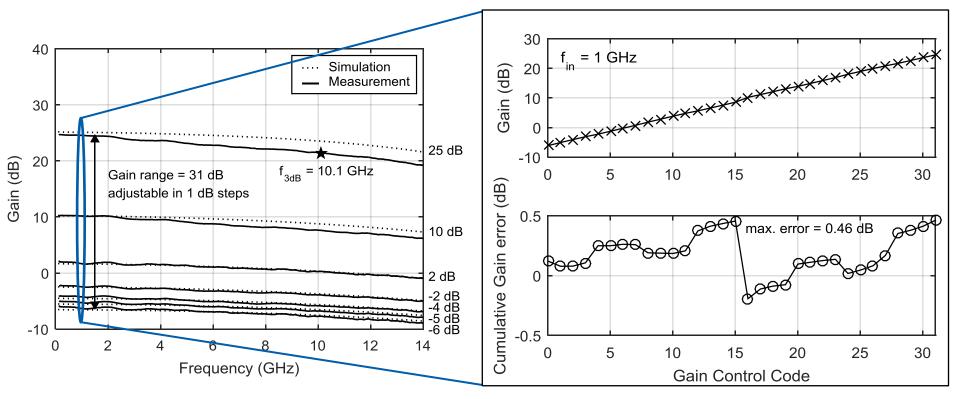

#### Die photograph **Specifications** G $C_2$ **C**0 C4 G implemented in Gain range: 31 dB in 0.13 μm SiGe BiCMOS 0.4 mm S S from IHP 1 dB steps S S -0.19/0.46 dB Gain accuracy: @ 1 GHz G DC C1 G >10.1 GH7 Bandwidth: 0.6 mm

European Microwave Week 2017

**Achievements**

- Low-complexity PGA architecture

- 31 dB gain range programmable in 1 dB steps

- Gain accuracy smaller than 0.46 dB

- >10.1 GHz 3-dB bandwidth

#### WS-03 | Wireless 100Gb/s and Beyond: Progress in Ultra-fast Wireless Communications

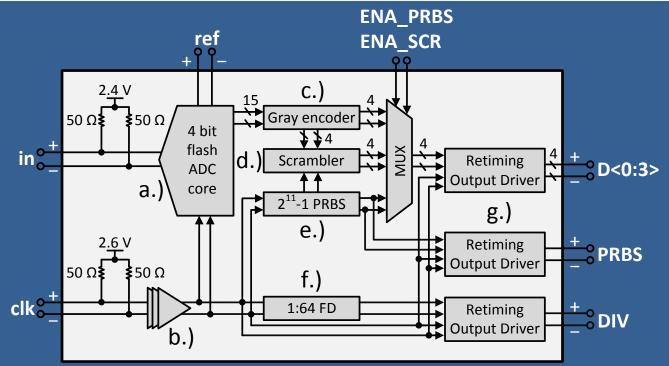

#### **SPARS ADC**

#### **ADC architecture**

- ADC ... Analog-to-Digital Converter

- PRBS ... Pseudo Random Bit Sequence

- FD ... Frequency Divider

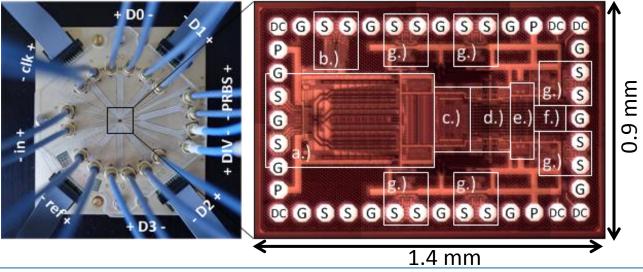

#### <u>RF PCB (left)</u> and die photograph (right)

implemented in 0.13 μm SiGe BiCMOS from IHP

#### **Measurement Results**

#### Achievements

- Enables sampling rates from DC to 42 GS/s

- => more than 60% speed

improvement to current stateof-the-art single-core ADCs with

digital encoder (25 GS/s)

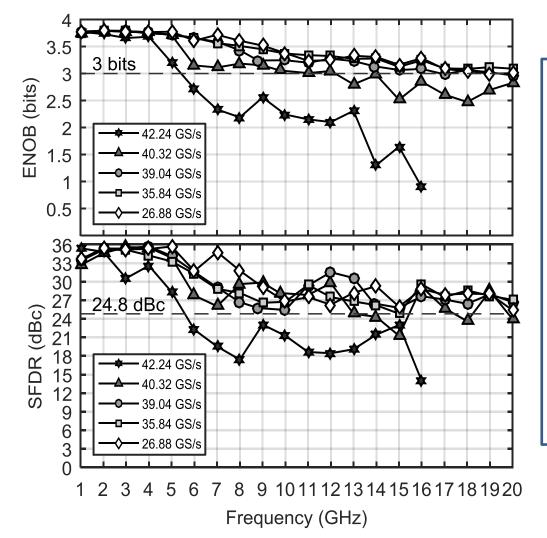

- ENOB > 3 bits and SFDR >24.8 dBc within DC-20 GHz frequency band up to 39 GS/s

- FOM = 8.3 pJ/conv.

- FOM . . . Figure of Merit

Real-time measurement with 70 GHz sub-sampling scope

European Microwave Week 2017

## Conclusion

- Novel transceiver architecture concept based on "Simultaneous Phase and Amplitude Regenerative Sampling"

- significantly reduced system size and power consumption (single-stage instead of multi-stage amplifiers, no receiver synthesizer, ...)

- verified to be competitive to homodyne system in terms of noise and data rate with scaled demonstrator

- mmW Super-Regenerative Oscillator for 180 GHz target frequency implemented and successfully verified

- Transmitter RFDAC concept investigated and implemented to exploit relaxed power level requirements from high SRO gain

- 4 bit ADC with up to 42 GS/s and outstanding performance as well as wideband baseband PGA demonstrated experimentally

- Next steps: Component integration to demonstrate mmW self-mixing receiver

#### **References (I)**

- C. Carlowitz and M. Vossiek, "Demonstration of an Efficient High Speed Communication Link Based on Regenerative Sampling," in Proceedings of the International Microwave Symposium (IMS2017), Honolulu, Hawaii, USA, June 2017.

- C. Carlowitz and M. Vossiek, "Concept for a Novel Low-Complexity QAM Transceiver Architecture Suitable for Close to Transition Frequency Operation," in Proceedings of the IEEE MTT-S International Microwave Symposium 2015 (IMS 2015), Phoenix, Arizona, USA, May 2015.

- C. Carlowitz and M. Vossiek, "PSK Modulator for Regenerative Sampling Gigabit UWB Communication," in Proceedings of the 8th German Microwave Conference (GeMiC2014), Aachen, Germany, Mar. 2014.

- C. Carlowitz, A. Esswein, R. Weigel and M. Vossiek, "Concepts for Generation of Angle Modulated mm-Wave UWB Signals for Communication and Ranging," presented at the IMS 2013 Workshop on RFICs/MMICs and Their Professional Wireless Sensing Applications, Seattle, USA, June 2013.

- C. Carlowitz, A. Esswein, R. Weigel and M. Vossiek, "Regenerative Sampling Self-Mixing Receiver: A Novel Concept for Low Complexity Phase Demodulation," in Proceedings of the IEEE International Microwave Symposium 2013, Seattle, USA, June 2013.

- H. Ghaleb, M. El-Shennawy, Udo Jörges, C. Carta, and F. Ellinger, "Nonlinear Modeling of Cross-Coupled Regenerative Sampling Oscillators," *IEEE PRIME*, 2017.

- H. Ghaleb, P. V. Testa, S. Schumann, C. Carta, and F. Ellinger, "A 160-GHz Switched Injection-Locked Oscillator for Phase and Amplitude Regenerative Sampling," accepted for publication in *IEEE MWCL*, 2017.

- H. Ghaleb, M. El-Shennawy, C. Carta, and F. Ellinger, "A 148-GHz Regenerative Sampling Oscillator," accepted for publication in *IEEE EuMIC*, 2017.

#### **References (II)**

- X.-Q. Du, A. Knobloch, M. Grözing, M. Buck and M. Berroth, "A DC to 10.1 GHz, 31 dB Gain Range Control, Digital Programmable Gain Amplifier," IEEE German Microwave Conference (GeMiC), Bochum, 2016, pp. 144-147.

- X.-Q. Du, A. Knobloch, M. Grözing, M. Buck and M. Berroth, "Analysis and Design of a Linear Digital Programmable Gain Amplifier," Frequenz, Degruyter, vol. 71, no. 3, pp. 143-150, Mar. 2017.

- M. Grözing, H. Huang, X.-Q. Du and M. Berroth, "Data converters for 100 Gbit/s communication links and beyond," IEEE Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Austin, TX, 2016, pp. 104-106.

- X.-Q. Du, M. Grözing, M. Buck and M. Berroth, "A 40 GS/s 4 bit SiGe BiCMOS Flash ADC," IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), to be published.

- T. Girg, D. Schrüfer, M. Dietz, A. Hagelauer, D. Kissinger, and R. Weigel, "Low Complexity 60-GHz Receiver Architecture for Simultaneous Phase and Amplitude Regenerative Sampling Systems" in International Symposium on Integrated Circuits, Singapur, 2016, pp. 1-4.

- T. Girg, C. Beck, M. Dietz, A. Hagelauer, D. Kissinger, and R. Weigel, "A 180 GHz Frequency Multiplier in a 130 nm SiGe BiCMOS Technology" in 2016 IEEE 14th International NEWCAS Conference, Vancouver, 2016, pp. 1-4.

- D. Kissinger, T. Girg, C. Beck, I. Nasr, H. Forstner, M. Wojnowski, K. Pressel, and R. Weigel, "Integrated millimeter-wave transceiver concepts and technologies for wireless multi-Gbps communication" in IEEE MTT-S International Microwave Symposium, Phoenix, AZ, 2015, pp. 1-3.

- A. Balteanu, P. Schvan and S. P. Voinigescu, "A 6-bit Segmented DAC Architecture With up to 56-GHz Sampling Clock and 6-Vpp Differential Swing," in IEEE Transactions on Microwave Theory and Techniques, vol. 64, no. 3, pp. 881-891, March 2016.